# 1100/70 Systems

# Processor and Storage

Hardware Programmer Reference

This document contains the latest information available at the time of preparation. Therefore, it may contain descriptions of functions not implemented at manual distribution time. To ensure that you have the latest information regarding levels of implementation and functional availability, please consult the appropriate release documentation or contact your local Sperry representative.

Sperry reserves the right to modify or revise the content of this document. No contractual obligation by Sperry regarding level, scope, or timing of functional implementation is either expressed or implied in this document. It is further understood that in consideration of the receipt or purchase of this document, the recipient or purchaser agrees not to reproduce or copy it by any means whatsoever, nor to permit such action by others, for any purpose without prior written permission from Sperry.

FASTRAND, SPERRY, SPERRY, SPERRY UNIVAC, SPERRY UNIVAC, UNISCOPE, UNISERVO, UNIVAC, and are registered trademarks of the Sperry Corporation. ESCORT, MAPPER, PAGEWRITER, PIXIE, SPERRYLINK, and UNIS are additional trademarks of the Sperry Corporation.

### Page Status Summary

| Section            | Pages  | Update |

|--------------------|--------|--------|

| Cover/Disclaimer   |        |        |

| PSS                | 1      |        |

| Contents           | 1 - 10 |        |

| Section 1          | 1      |        |

| Section 2          | 1 - 12 |        |

| Section 3          | 1 - 19 |        |

| Section 4          | 1 - 33 |        |

| Section 5          | 1 - 8  |        |

| Section 6          | 1 - 30 |        |

| Section 7          | 1 - 11 |        |

| Section 8          | 1 - 29 |        |

| Section 9          | 1 - 85 |        |

| Appendix A         | 1 - 10 |        |

| Appendix B         | 1 - 12 |        |

| Appendix C         | 1 - 18 |        |

| Appendix D         | 1 - 7  |        |

| Index              | 1 - 11 |        |

| User Comment Sheet |        |        |

|                    |        |        |

|                    |        |        |

|                    |        | İ      |

|                    |        |        |

|                    |        | į      |

|                    |        |        |

| Section | Pages | Update |

|---------|-------|--------|

|         | ·     |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       | ;      |

|         |       |        |

|         |       |        |

| 4       |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

| :       |       |        |

|         |       |        |

|         | -     |        |

|         |       |        |

|         |       |        |

# Contents

# Page Status Summary

## Contents

| 1. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 1–1                                                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | 1.1. General                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1                                                                |

|    | 1.2. Scope                                                                                                                                                                                                                                                                                                                                                                                                                      | 1–1                                                                |

| 2. | Systems Description                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1                                                                |

|    | 2.1. General                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1                                                                |

|    | <ul> <li>2.2. System Components</li> <li>2.2.1. Central Processing Unit (CPU)</li> <li>2.2.2. Input/Output Unit (IOU)</li> <li>2.2.3. Main Storage Unit (MSU)</li> <li>2.2.4. Storage Interface Unit (SIU)</li> <li>2.2.5. Support Controller</li> <li>2.2.6. System Support Processor (SSP)/Console</li> <li>2.2.7. System Console</li> <li>2.2.8. Attached Virtual Processor</li> <li>2.2.9. Peripheral Subsystems</li> </ul> | 2-2<br>2-2<br>2-3<br>2-3<br>2-4<br>2-5<br>2-5<br>2-5<br>2-6<br>2-6 |

|    | 2.3. Additional Features 2.3.1. Extended Instruction Set Feature 2.3.2. Performance Monitoring Feature 2.3.3. Logic Analyzer 2.3.4. Subsystem Partitioning Features                                                                                                                                                                                                                                                             | 2-6<br>2-6<br>2-6<br>2-7<br>2-7                                    |

|    | <ul> <li>2.4. System Configuration</li> <li>2.4.1. Unit Processor Configuration</li> <li>2.4.2. Dual Processor Configuration</li> <li>2.4.3. Multiprocessor Configuration</li> <li>2.4.4. Minimum Peripheral Complement</li> </ul>                                                                                                                                                                                              | 2-7<br>2-7<br>2-8<br>2-9<br>2-11                                   |

| <b>5.</b> | Central Processing Unit                                                                                                    | 3–1                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|           | 3.1. General                                                                                                               | 3–1                             |

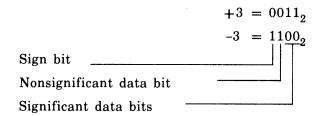

|           | 3.2. Arithmetic Section 3.2.1. General Operation 3.2.1.1. Data Word 3.2.1.2. Data Word Complement 3.2.1.3. Absolute Values | 3-1<br>3-1<br>3-2<br>3-2<br>3-2 |

|           | 3.2.2. Microprogrammed Control                                                                                             | 3-2                             |

|           | 3.2.3. Main Adder Characteristics                                                                                          | 3-3                             |

|           | 3.2.4. Fixed-Point Single- or Double-Precision Add or Subtract Overflow                                                    | • •                             |

|           | and Carry                                                                                                                  | 3-3                             |

|           | 3.2.4.1. Overflow                                                                                                          | 3-3                             |

|           | 3.2.4.2. Carry                                                                                                             | 3–3                             |

|           | 3.2.4.3. Arithmetic Interrupt                                                                                              | 3-5                             |

|           | 3.2.5. Fixed-Point Division                                                                                                | 3-5                             |

|           | 3.2.6. Fixed-Point Multiplication                                                                                          | 3-5                             |

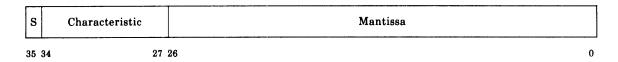

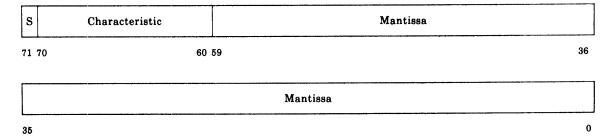

|           | 3.2.7. Floating-Point Arithmetic                                                                                           | 3-5                             |

|           | 3.2.8. Floating-Point Numbers and Word Formats 3.2.8.1. Single-Precision Floating-Point Numbers                            | 3-6                             |

|           | 3.2.8.2. Double-Precision Floating-Point Numbers                                                                           | 3–7<br>3–8                      |

|           | 3.2.8.3. Negative Floating-Point Numbers                                                                                   | 3-8                             |

|           | 3.2.8.4. Residue                                                                                                           | 3-8                             |

|           | 3.2.9. Normalized/Unnormalized Floating-Point Numbers                                                                      | 3-9                             |

|           | 3.2.10. Floating-Point Characteristic Overflow/Underflow                                                                   | 3-9                             |

|           | 3.2.10.1. Floating-Point Characteristic Overflow                                                                           | 3-9                             |

|           | 3.2.10.2. Floating-Point Characteristic Underflow                                                                          | 3-10                            |

|           | 3.2.10.3. Floating-Point Divide Fault                                                                                      | 3-10                            |

|           | 3.2.11. Fixed-Point to Floating-Point Conversion                                                                           | 3–10                            |

|           | 3.2.12. Floating-Point Addition                                                                                            | 3–11                            |

|           | 3.2.13. Double-Precision Floating-Point Addition                                                                           | 3–11                            |

|           | 3.2.14. Floating-Point Subtraction (Add Negative)                                                                          | 3-11                            |

|           | 3.2.15. Floating-Point Multiplication                                                                                      | 3–12                            |

|           | 3.2.16. Floating-Point Division                                                                                            | 3–12<br>3–12                    |

|           | 3.2.17. Floating-Point Zero                                                                                                | 3-12                            |

|           | 3.3. Control Section                                                                                                       | 3–12                            |

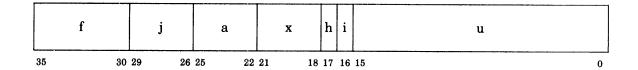

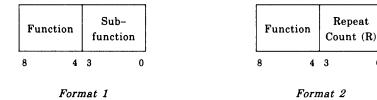

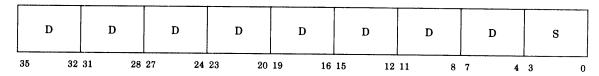

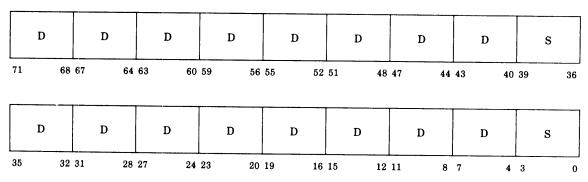

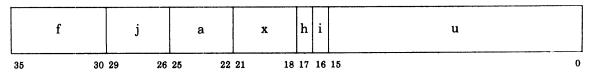

|           | 3.3.1. Instruction Word Format                                                                                             | 3–12                            |

|           | 3.3.2. Instruction Word Fields                                                                                             | 3-13                            |

|           | 3.3.2.1. Function Code (f-field)                                                                                           | 3-13                            |

|           | 3.3.2.2. Operand Qualifier or Extended Function Code (j-field)                                                             | 3–13                            |

|           | 3.3.2.3. Register Operand Address (a-field) 3.3.2.4. Index Register Address (x-field)                                      | 3–17<br>3–17                    |

|           | 3.3.2.5. Index Register Address (x-field) 3.3.2.5. Index Incrementation Designator (h-field)                               | 3-17                            |

|           | 3.3.2.6. Indirect Addressing Designator (i-field)                                                                          | 3-17                            |

|           | 3.3.2.7. Operand Address Displacement (u-field)                                                                            | 3–18                            |

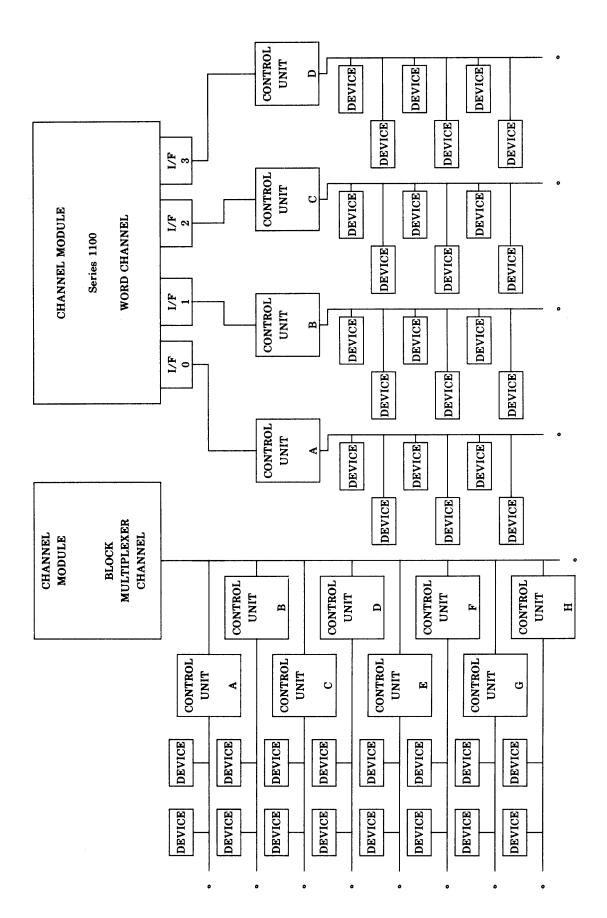

| 1.        | Input/Output Unit                                                                                                          | 4–1                             |

|           | 4.1. General                                                                                                               | 4-1                             |

|           | 4.2. Functional Characteristics                                                                                            | 4–1                             |

|           | 4.2.1. Channels                                                                                                            | 4-3                             |

|           | 4.2.2. Subchannels                                                                                                         | 4-3                             |

|            | 4.3. Control of Input/Output Devices 4.3.1. Input/Output Device Addressing | 4-3          |

|------------|----------------------------------------------------------------------------|--------------|

|            | 4.3.2. States of the Input/Output System                                   | 4-5          |

|            | 4.3.3. Condition Codes                                                     | 4-6          |

|            | 4.3.4. Instruction Format and Channel Address Word                         | 4-6          |

|            | 4.3.4.1. Start I/O Fast Release - SIOF f=75, j=01                          | 4-6          |

|            | 4.3.4.2. Test Subchannel – TSC 75,03                                       | 4-10         |

|            | 4.3.4.3. Halt Device – HDV 75,04                                           | 4-11<br>4-12 |

|            | 4.3.4.4. Halt Channel – HCH 75,05                                          | 4-12<br>4-13 |

|            | 4.3.4.5. Load Channel Register – LCR 75,10                                 | 4-13<br>4-14 |

|            | 4.3.5. IOU Control Words                                                   | 4-15         |

|            | 4.3.5.1. Channel Address Words                                             | 4-15         |

|            | 4.3.5.2. Channel Command Words                                             | 4–15         |

|            | 4.3.5.2.1. ISI Word Interface CCW                                          | 4-16         |

|            | 4.3.5.2.2. ESI Word Interface CCW                                          | 4-17         |

|            | 4.3.5.2.3. Block Multiplexer Channel CCW                                   | 4-20         |

|            | 4.3.5.2.4. Status Table Subchannel CCW                                     | 4-22         |

|            | 4.4. Execution of I/O Operations                                           | 4-25         |

|            | 4.5. Transfer In Channel (TIC) Command                                     | 4-26         |

|            | 4.6. Chaining Operations                                                   | 4.00         |

|            | 4.6.1. Data Chaining                                                       | 4-26<br>4-26 |

|            | 4.6.2. Command Chaining                                                    | 4-26<br>4-27 |

|            | 4.6.3. EI Chaining (ESI Word Interface Only)                               | 4-28         |

|            | 4.6.4. Truncated Search (Block Multiplexer Channel Only)                   | 4-28         |

|            | 4.7. Interrupt Generation Flag                                             | 4-29         |

|            | 4.7.1. Monitor (Word Channel and Status Table Subchannel)                  | 4-29         |

|            | 4.7.2. ISI Monitor Conditions                                              | 4-30         |

|            | 4.7.3. ESI Subchannel Conditions                                           | 4-30         |

|            | 4.7.4. Status Table Subchannel Monitor Conditions                          | 4–30         |

|            | 4.8. Status                                                                | 4-30         |

|            | 4.9. Initial Load                                                          | 4-32         |

|            | 4.10. Word Channel Back-to-Back Operations                                 | 4-32         |

|            | 4.11. Priorities                                                           | 4-32         |

|            | 4.12. Basic Programming Procedure                                          | 4–33         |

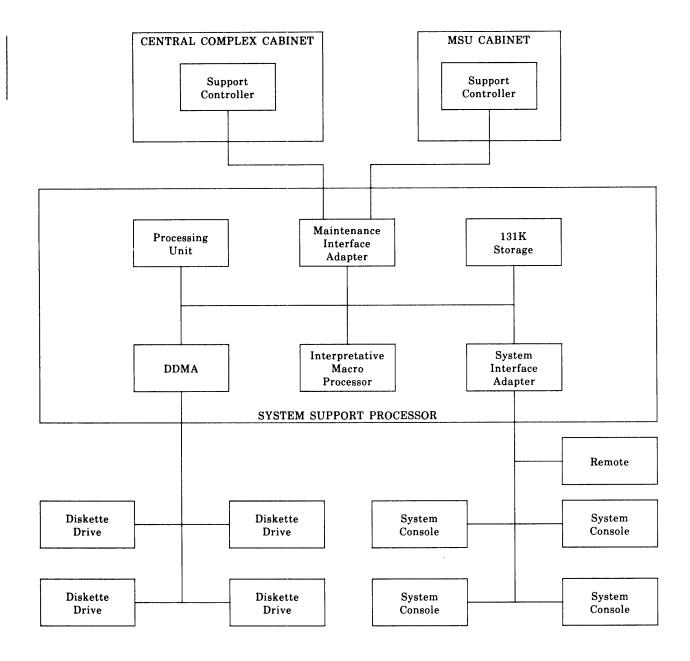

| <b>5</b> . | System Support Processor                                                   | 5–1          |

|            | 5.1. General                                                               | 5–1          |

|            | 5.2. System Communications                                                 | 5–2          |

|            | 5.9 Functions Controlled to COD                                            |              |

|            | 5.3. Functions Controlled by the SSP                                       | 5-3          |

|            | 5.3.1. Partitioning                                                        | 5-3          |

|            | 5.3.2. System Initial Program Load 5.3.3. Automatic Recovery               | 5-3          |

|            | 5.3.4. CPU Fault Analysis                                                  | 5-4          |

|            | o.o.i. of o faut maryon                                                    | 5–4          |

|    | 5.3.5. Performance Monitoring 5.3.6. Logic Analyzer Control   | 5-4<br>5-7   |

|----|---------------------------------------------------------------|--------------|

|    | 5.3.7. System Control                                         | 5–8          |

| 6. | Storage Systems                                               | 6–1          |

|    | 6.1. General                                                  | 6–1          |

|    | 6.2. Storage Interface Unit                                   | 6–1          |

|    | 6.2.1. Functional Units                                       | 6-3          |

|    | 6.2.1.1. CPU Interface Section                                | 6-3          |

|    | 6.2.1.2. Resident Directory and Directory Control Section     | 6-4          |

|    | 6.2.1.3. Main Storage Interface Section                       | 6-4          |

|    | 6.2.1.4. SIU Main Control Section                             | 6–5          |

|    | 6.2.1.5. System Support Interface                             | 6–5          |

|    | 6.2.1.6. Invalidate Interface                                 | 6-5          |

|    | 6.2.1.7. System Clock Interface                               | 6-5          |

|    | 6.2.1.8. Data Buffer                                          | 6-5          |

|    | 6.2.2. Performance                                            | 6-6          |

|    | 6.2.3. Error Detection and Reporting                          | 6–6          |

|    | 6.2.3.1. Storage Check Interrupt Status Request Formats       | 6–6          |

|    | 6.2.3.2. CPU Errors                                           | 6-8          |

|    | 6.2.3.3. Internal SIU Errors                                  | 6-9          |

|    | 6.2.3.4. SIU/Main Storage Interface Errors                    | 6–10         |

|    | 6.2.3.5. Main Storage Errors                                  | 6–10         |

|    | 6.2.3.6. Invalidate Interface Errors                          | 6-11         |

|    | 6.2.3.7. Maintenance Interface Errors                         | 6-11         |

|    | 6.2.4. Storage Lock                                           | 6–13         |

|    | 6.3. Main Storage Unit                                        | 6-13         |

|    | 6.3.1. Modes of Operation                                     | 6–14         |

|    | 6.3.1.1. Online Operation                                     | 6–14         |

|    | 6.3.1.2. Offline Operations                                   | 6–15         |

|    | 6.3.2. Operational Characteristics                            | 6–15         |

|    | 6.3.2.1. Data Format                                          | 6–15         |

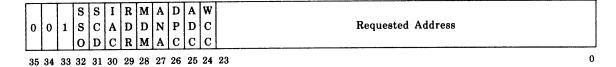

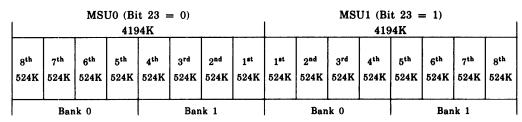

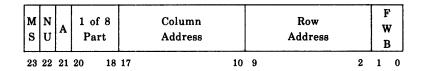

|    | 6.3.2.2. Address Format                                       | 6–16         |

|    | 6.3.2.3. Initialize                                           | 6–17         |

|    | 6.3.2.4. Fault Detection and Correction                       | 6–17         |

|    | 6.3.2.5. Correction Logging                                   | 6–18         |

|    | 6.3.2.6. Status Word Reporting                                | 6-18         |

|    | 6.3.2.7. Status Word Through Checking (External Storage Only) | 6-19         |

|    | 6.3.2.8. MSU Single-Bit Error and Special Code Reporting      | 6-19         |

|    | 6.3.2.9. MSU Fault Injection                                  | 6-20         |

|    | 6.3.2.10. Storage Lock                                        | 6-22         |

|    | 6.3.2.11. System Synchronization                              | 6-22         |

|    | 6.3.3. Fault Handling                                         | 6-22<br>6-25 |

|    | 6.3.4. Fixed Address Assignments                              | 0-25         |

|    | 6.4. General Register Stack                                   | 6-27         |

|    | 6.4.1. Index (X) Registers                                    | 6-28         |

|    | 6.4.2. Arithmetic (A) Registers                               | 6-29         |

|    | 6.4.3. Special (R) Registers                                  | 6-29         |

|    | 6.4.3.1. Real-Time Clock (R0)                                 | 6-29<br>6-29 |

|    | 6.4.3.2. Repeat Count Register (R1)                           | 6-29<br>6-29 |

|    | 6.4.3.3. Masked Register (R2)                                 | 0-29         |

|    | <ul> <li>6.4.4. CPU State Control Registers</li> <li>6.4.5. Unassigned Registers</li> <li>6.4.6. Control Register Selection Designator</li> <li>6.4.7. Special GRS Notes</li> </ul>                                                                                                                                                                                                                                       | 6-29<br>6-30<br>6-30<br>6-30                                 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 7. | Executive Control                                                                                                                                                                                                                                                                                                                                                                                                         | 7–1                                                          |

|    | 7.1. General                                                                                                                                                                                                                                                                                                                                                                                                              | 7–1                                                          |

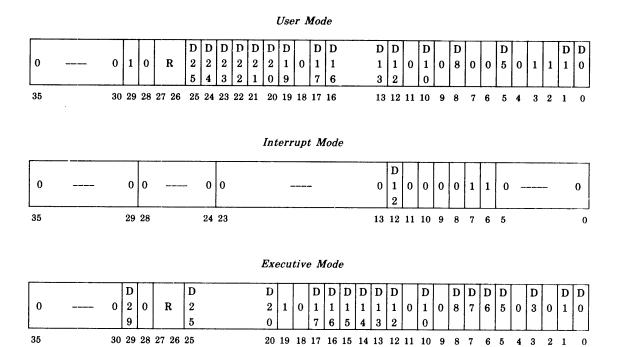

|    | 7.2. CPU State 7.2.1. Designator Register 7.2.2. Dayclock                                                                                                                                                                                                                                                                                                                                                                 | 7-1<br>7-1<br>7-6                                            |

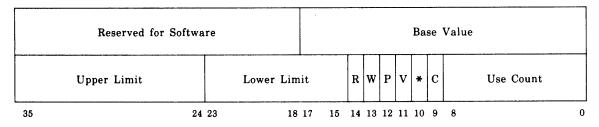

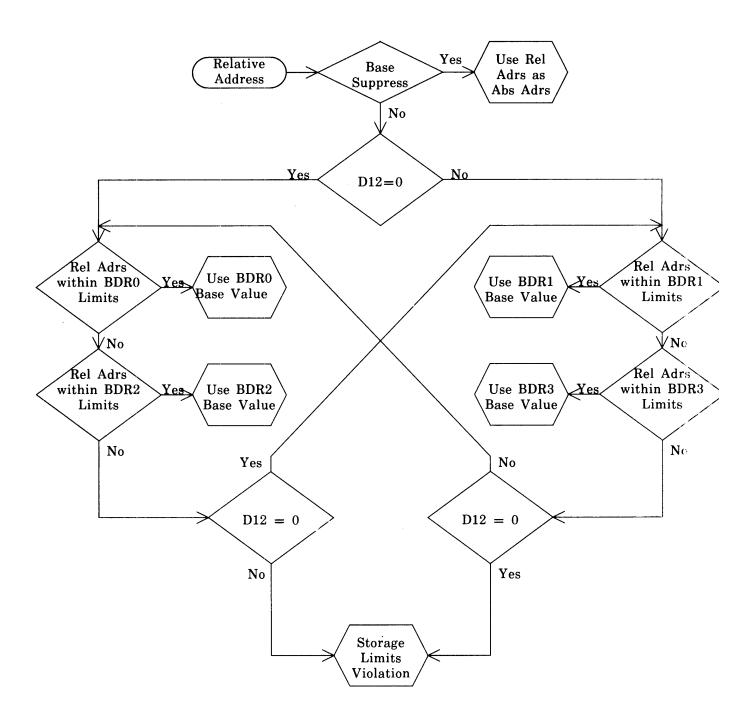

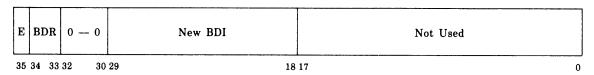

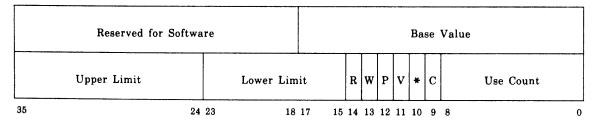

|    | <ul> <li>7.3. Address Formation</li> <li>7.3.1. Bank Descriptor</li> <li>7.3.2. Limits</li> <li>7.3.3. Control Information</li> <li>7.3.4. Bank Descriptor Registers</li> <li>7.3.5. Address Generation</li> </ul>                                                                                                                                                                                                        | 7-7<br>7-8<br>7-9<br>7-9<br>7-9<br>7-10                      |

| 8. | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                | 8-1                                                          |

|    | 8.1. General                                                                                                                                                                                                                                                                                                                                                                                                              | 8–1                                                          |

|    | <ul> <li>8.2. Interrupt Sequence</li> <li>8.2.1. Program Status</li> <li>8.2.2. Addressing Status</li> <li>8.2.3. Interrupt Status</li> </ul>                                                                                                                                                                                                                                                                             | 8-3<br>8-3<br>8-4<br>8-5                                     |

|    | <ul> <li>8.3. Interrupt Types</li> <li>8.3.1. Program Exception Interrupts</li> <li>8.3.2. Arithmetic Exception Interrupts</li> <li>8.3.3. Program-Initiated Interrupts</li> <li>8.3.4. Interprocessor Interrupt</li> <li>8.3.5. Clock Interrupts</li> <li>8.3.6. Immediate Storage Check Interrupts</li> <li>8.3.7. Delayed Storage Check Interrupts</li> <li>8.3.8. Multiprocessor Interrupt Synchronization</li> </ul> | 8-5<br>8-5<br>8-8<br>8-9<br>8-9<br>8-10<br>8-14<br>8-18      |

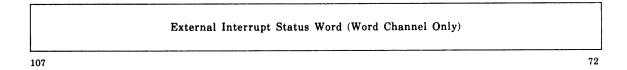

|    | 8.4. Input/Output Interrupts 8.4.1. Machine Check Interrupts 8.4.2. Normal Interrupts 8.4.2.1. ISI Word Interface CSW 8.4.2.2. Block Multiplexer CSW 8.4.2.3. Status Table Subchannel CSW 8.4.2.4. Test Subchannel CSW 8.4.3. Table Interrupts                                                                                                                                                                            | 8-18<br>8-18<br>8-20<br>8-20<br>8-22<br>8-24<br>8-25<br>8-27 |

| 9. | Instruction Repertoire                                                                                                                                                                                                                                                                                                                                                                                                    | 9–1                                                          |

|    | 9.1. General                                                                                                                                                                                                                                                                                                                                                                                                              | 9–1                                                          |

|    | 9.2. Load Instructions<br>9.2.1. Load A - L,LA 10<br>9.2.2. Load Negative A - LN,LNA 11                                                                                                                                                                                                                                                                                                                                   | 9-2<br>9-2<br>9-2                                            |

| 9.2.3. Load Magnitude A - LM,LMA 12                                                                               | 9-2          |

|-------------------------------------------------------------------------------------------------------------------|--------------|

| 9.2.4. Load Negative Magnitude A - LNMA 13                                                                        | 9-2          |

| 9.2.5. Load R - L,LR 23                                                                                           | 9-3          |

| 9.2.6. Load X Modifier - LXM 26                                                                                   | 9-3          |

| 9.2.7. Load X - L,LX 27                                                                                           | 9-3          |

| 9.2.8. Load X Increment – LXI 46                                                                                  | 9-3          |

| 9.2.9. Double Load A - DL $f = 71$ , $j = 13$                                                                     | 9-3          |

| 9.2.10. Double Load Negative A – DLN 71,14                                                                        | 9-4          |

| 9.2.10. Double Load Negative A - DIN 71,14                                                                        | 9-4          |

| 9.2.11. Double Load Magnitude A - DLM 71,15                                                                       | 3-4          |

| 0.2 Store Instructions                                                                                            | 9-4          |

| 9.3. Store Instructions                                                                                           | 9-4          |

| 9.3.1. Store A - S,SA 01                                                                                          | 9-4<br>9-4   |

| 9.3.2. Store Negative A - SN,SNA 02                                                                               |              |

| 9.3.3. Store Magnitude A - SM,SMA 03                                                                              | 9-5          |

| 9.3.4. Store R - S,SR 04                                                                                          | 9-5          |

| 9.3.5. Store Constant Instructions - XX 05; a = 00-07                                                             | 9-5          |

| 9.3.6. Store X - S,SX 06                                                                                          | 9–5          |

| 9.3.7. Double Store A - DS 71,12                                                                                  | 9-5          |

| 9.3.8. Block Transfer - BT 22                                                                                     | 9-6          |

|                                                                                                                   |              |

| 9.4. Fixed-Point Arithmetic Instructions                                                                          | 9–6          |

| 9.4.1. Add to A - A,AA 14                                                                                         | 9–7          |

| 9.4.2. Add Negative to A - AN,ANA 15                                                                              | 9-7          |

| 9.4.3. Add Magnitude to A - AM,AMA 16                                                                             | 9-7          |

| 9.4.4. Add Negative Magnitude to A - ANM, ANMA 17                                                                 | 9–7          |

| 0.4.5 Add Ilmon AII 20                                                                                            | 9-8          |

| 9.4.6. Add Negative Upper - ANU 21                                                                                | 9-8          |

| 9.4.6. Add Negative Upper - ANU 21 9.4.7. Add to X - A,AX 24 9.4.8. Add Negative to X - AN,ANX 25                 | 9-8          |

| 9.4.8. Add Negative to X - AN.ANX 25                                                                              | 9-8          |

| 9.4.9. Multiply Integer - MI 30                                                                                   | 9-8          |

| 9.4.10. Multiply Single Integer – MSI 31                                                                          | 9-8          |

| 9.4.11. Multiply Fractional – MF 32                                                                               | 9-9          |

| 9.4.12. Divide Integer - DI 34                                                                                    | 9-9          |

|                                                                                                                   | 9-9          |

| • · - · - · · · · · · · · · · · · · · ·                                                                           | 9-10         |

| • · • · • · • · · · · · · · · · · · · ·                                                                           | 9-10         |

| 9.4.15. Double-Precision Fixed-Point Add - DA 71,10 9.4.16. Double-Precision Fixed-Point Add Negative - DAN 71,11 | 9-10         |

|                                                                                                                   | 9-10         |

| 9.4.17. Add Halves – AH 72,04                                                                                     |              |

| 9.4.18. Add Negative Halves - ANH 72,05                                                                           | 9-11         |

| 9.4.19. Add Thirds - AT 72,06                                                                                     | 9–11         |

| 9.4.20. Add Negative Thirds - ANT 72,07                                                                           | 9–11         |

| O. F. Division Daint Anithmentia Instructions                                                                     | 0 11         |

| 9.5. Floating-Point Arithmetic Instructions                                                                       | 9–11<br>9–12 |

| 9.5.1. Floating Add - FA 76,00                                                                                    |              |

| 9.5.2. Floating Add Negative - FAN 76,01                                                                          | 9-12         |

| 9.5.3. Double-Precision Floating Add - DFA 76,10                                                                  | 9-12         |

| 9.5.4. Double-Precision Floating Add Negative - DFAN 76,11                                                        | 9-13         |

| 9.5.5. Floating Multiply - FM 76,02                                                                               | 9–13         |

| 9.5.6. Double-Precision Floating Multiply - DFM 76,12                                                             | 9–14         |

| 9.5.7. Floating Divide - FD 76,03                                                                                 | 9-15         |

| 9.5.8. Double-Precision Floating Divide - DFD 76,13                                                               | 9–16         |

| 9.5.9. Load and Unpack Floating - LUF 76,04                                                                       | 9-16         |

| 9.5.10. Double Load and Unpack Floating - DFU 76,14                                                               | 9–17         |

| 9.5.11. Load and Convert to Floating - LCF 76,05                                                                  | 9–17         |

| 9.5.12. Double Load and Convert to Floating - DFP, DLCF 76,15                                                     | 9-17         |

| 9.5.13. Floating Expand and Load FEL 76,16                                                                       | 9-18         |

|------------------------------------------------------------------------------------------------------------------|--------------|

| 9.5.14. Floating Compress and Load - FCL 76,17<br>9.5.15. Magnitude of Characteristic Difference to Upper - MCDU | 9–19         |

| 76,06                                                                                                            | 9–19         |

| 9.5.16. Characteristic Difference to Upper - CDU 76,07                                                           | 9-19<br>9-20 |

| 5.5.10. Characteristic Difference to Opper - CDO 70,07                                                           | 9-20         |

| 9.6. Search and Masked-Search Instructions                                                                       | 9-20         |

| 9.6.1. Search Equal - SE 62                                                                                      | 9-22         |

| 9.6.2. Search Not Equal - SNE 63                                                                                 | 9-23         |

| 9.6.3. Search Less Than or Equal/Search Not Greater - SLE, SNG                                                   | 9-23         |

| 64                                                                                                               |              |

| 9.6.4. Search Greater - SG 65                                                                                    | 9-23         |

| 9.6.5. Search Within Range - SW 66                                                                               | 9-24         |

| 9.6.6. Search Not Within Range - SNW 67                                                                          | 9-24         |

| 9.6.7. Masked Search Equal - MSE 71,00                                                                           | 9-25         |

| 9.6.8. Masked Search Not Equal - MSNE 71,01                                                                      | 9-25         |

| 9.6.9. Masked Search Less Than or Equal/Not Greater - MSLE, MSNG                                                 |              |

| 71,02                                                                                                            | 9-26         |

| 9.6.10. Masked Search Greater - MSG 71,03                                                                        | 9-26         |

| 9.6.11. Masked Search Within Range - MSW 71,04                                                                   | 9-27         |

| 9.6.12. Masked Search Not Within Range - MSNW 71,05                                                              | 9-27         |

| 9.6.13. Masked Alphanumeric Search Less Than or Equal - MASL                                                     |              |

| 71,06                                                                                                            | 9-28         |

| 9.6.14. Masked Alphanumeric Search Greater - MASG 71,07                                                          | 9–29         |

| 9.7. Test (or Skip) Instructions                                                                                 | 9-29         |

| 9.7.1. Test Even Parity - TEP 44                                                                                 | 9-29         |

| 9.7.2. Test Odd Parity - TOP 45                                                                                  | 9-30         |

| 9.7.3. Test Less Than or Equal/Test Not Greater Than Modifier -                                                  | 0 00         |

| TLEM, TNGM 47                                                                                                    | 9-30         |

| 9.7.4. Test Zero - TZ 50                                                                                         | 9-30         |

| 9.7.5. Test Nonzero - TNZ 51                                                                                     | 9-31         |

| 9.7.6. Test Equal - TE 52                                                                                        | 9-31         |

| 9.7.7. Test Not Equal - TNE 53                                                                                   | 9-31         |

| 9.7.8. Test Less Than or Equal/Test Not Greater - TLE, TNG 54                                                    | 9-31         |

| 9.7.9. Test Greater - TG 55                                                                                      | 9-32         |

| 9.7.10. Test Within Range - TW 56                                                                                | 9-32         |

| 9.7.11. Test Not Within Range - TNW 57                                                                           | 9-32         |

| 9.7.12. Test Positive - TP 60                                                                                    | 9-33         |

| 9.7.13. Test Negative - TN 61                                                                                    | 9-33         |

| 9.7.14. Double-Precision Test Equal - DTE 71,17                                                                  | 9-33         |

| 9.8. Shift Instructions                                                                                          | 0 33         |

| 9.8.1. Single Shift Circular - SSC 73,00                                                                         | 9-33<br>9-35 |

| 9.8.2. Double Shift Circular - DSC 73,00                                                                         |              |

| 9.8.3. Single Shift Logical - SSL 73,02                                                                          | 9-35<br>9-35 |

| 9.8.4. Double Shift Logical - DSL 73,02                                                                          |              |

| 9.8.5. Single Shift Algebraic - SSA 73,04                                                                        | 9-36<br>9-36 |

| 9.8.6. Double Shift Algebraic - DSA 73,05                                                                        |              |

| 9.8.7. Load Shift and Count – LSC 73,06                                                                          | 9-36<br>9-36 |

| 9.8.8. Double Load Shift and Count - DLSC 73,00                                                                  | 9-36<br>9-37 |

| 9.8.9. Left Single Shift Circular - LSSC 73,07                                                                   | 9-37<br>9-37 |

| 9.8.10. Left Double Shift Circular - LDSC 73,11                                                                  | 9–37<br>9–37 |

| 9.8.11. Left Single Shift Logical - LSSL 73,11                                                                   | 9-37<br>9-37 |

| 9.8.12 Left Double Shift Logical - LDSL 73.12                                                                    | 9-31         |

| 9.9. Unconditional Jump Instructions                      | 9-38 |

|-----------------------------------------------------------|------|

| 9.9.1. Store Location and Jump - SLJ 72,01                | 9-38 |

| 9.9.2. Load Modifier and Jump - LMJ 74,13                 | 9–39 |

| 9.9.3. Allow All Interrupts and Jump - AAIJ 74,07         | 9–39 |

| 9.10. Bank Descriptor Selection Instructions              | 9-39 |

| 9 10 1 Load Bank and Jump - LBJ 07.17                     | 9-39 |

| 9.10.2. Load I-Bank Base and Jump - LIJ 07,13             | 9-40 |

| 9.10.3. Load D-Bank Base and Jump - LDJ 07,12             | 9-41 |

| 9.11. Conditional Jump Instructions                       | 9-41 |

| 9.11.1. Jump Greater and Decrement - JGD 70               | 9-41 |

| 9.11.2. Double-Precision Jump Zero - DJZ 71,16            | 9-41 |

| 9.11.3. Jump Positive and Shift - JPS 72,02               | 9-41 |

| 9.11.4. Jump Negative and Shift - JNS 72,03               | 9-42 |

| 9.11.5. Jump Zero - JZ 74,00                              | 9-42 |

| 9.11.6. Jump Nonzero - JNZ 74,01                          | 9-42 |

| 9.11.7. Jump Positive - JP 74,02                          | 9-42 |

| 9.11.8. Jump Negative - JN 74,03                          | 9-42 |

| 9.11.9. Jump/Jump Keys - J,JK 74,04                       | 9-43 |

| 9.11.10. Halt Jump/Halt Keys and Jump - HJ,HKJ 74,05      | 9-43 |

| 9.11.11. Jump No Low Bit - JNB 74,10                      | 9-43 |

| 9.11.12. Jump Low Bit - JB 74,11                          | 9-44 |

| 9.11.13. Jump Modifier Greater and Increment - JMGI 74,12 | 9-44 |

| 9.11.14. Jump Overflow – $J0 	 74,14$ ; $a = 0$           | 9-44 |

| 9.11.15. Jump Floating Underflow - JFU 74,14,01           | 9-44 |

| 9.11.16. Jump Floating Overflow - JFO 74,14,02            | 9-45 |

| 9.11.17. Jump Divide Fault - JDF 74,14,03                 | 9-45 |

| 9.11.18. Jump No Overflow - JNO 74,15,00                  | 9-45 |

| 9.11.19. Jump No Floating Underflow – JNFU 74,15,01       | 9-45 |

| 9.11.20. Jump No Floating Overflow - JNFO 74,15,02        | 9-45 |

| 9.11.21. Jump No Divide Fault - JNDF 74,15,03             | 9-45 |

| 9.11.22. Jump Carry - JC 74,16                            | 9-46 |

| 9.11.23. Jump No Carry – JNC 74,17                        | 9-46 |

| 9.12. Logical Instructions                                | 9-46 |

| 9.12.1. Logical OR - OR 40                                | 9-47 |

| 9.12.2. Logical Exclusive OR - XOR 41                     | 9-47 |

| 9.12.3. Logical AND - AND 42                              | 9-47 |

| 9.12.4. Masked Load Upper - MLU 43                        | 9-48 |

| 9.13. Miscellaneous Instructions                          | 9-48 |

| 9.13.1. Load DR Designators - LPD 07,14                   | 9-48 |

| 9.13.2. Store DR Designators - SPD 07,15                  | 9-48 |

| 9.13.3. Execute - EX 72,10                                | 9-48 |

| 9.13.4. Executive Request - ER 72,11                      | 9-49 |

| 9.13.5. Test and Set $-$ TS $73,17$ ; $a = 00$            | 9-49 |

| 9.13.6. Test and Set and Skip - TSS 73,17,01              | 9-50 |

| 9.13.7. Test and Clear and Skip - TCS 73,17; a = 02       | 9-50 |

| 9.13.8. No Operation - NOP 74,06                          | 9-50 |

| 9.13.9. Store Register Set - SRS 72,16                    | 9-50 |

| 9.13.10. Load Register Set - LRS 72,17                    | 9-51 |

| 9.13.11. Test Relative Address - TRA 72,15                | 9-51 |

| 9.13.12. Increase Instructions - XX 05: $a = 10-17$       | 9-52 |

| 9.14. Optional Extended Instruction Set                                                                                                  | 9-53 |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 9.14.1. Bit Move - BIM 37.10                                                                                                             | 9-53 |

| 9.14.2. Bit Compare - BIC 37,11                                                                                                          | 9–55 |

| 9.14.3. Extended Bit Instructions                                                                                                        | 9-56 |

| 9.14.3.1. Bit Move with Translation and Control - BMTC 37,12                                                                             | 9-56 |

| 9.14.3.2. Bit Compare Long - BICL 37,13                                                                                                  | 9-61 |

| 9.14.3.3. Bit Move Long - BIML 37,14                                                                                                     | 9-63 |

| 9.14.4. Byte to Decimal - BDE 37,15                                                                                                      | 9-64 |

| 9.14.5. Decimal to Byte - DEB 37,16                                                                                                      | 9-66 |

| 9.14.6. Edit Decimal - EDDE 37,17                                                                                                        | 9-68 |

| 9.14.7. Decimal Instructions                                                                                                             | 9-74 |

| 9.14.7.1. Add Decimal - ADE 07,00                                                                                                        | 9-76 |

| 9.14.7.2. Double Add Decimal - DADE 07,01                                                                                                | 9-76 |

| 9.14.7.3. Subtract Decimal - SDE 07,02                                                                                                   | 9-76 |

| 9.14.7.4. Double Subtract Decimal - DSDE 07.03                                                                                           | 9-76 |

| 9.14.7.5. Decimal to Integer - DEI 07.06                                                                                                 | 9-76 |

| 9.14.7.6. Double Decimal to Integer - DDEI 07,07                                                                                         | 9-76 |

| 9.14.7.5. Decimal to Integer - DEI 07,06<br>9.14.7.6. Double Decimal to Integer - DDEI 07,07<br>9.14.7.7. Integer to Decimal - IDE 07,10 | 9-77 |

| 9.14.7.8. Double Integer to Decimal - DIDE 07,11                                                                                         | 9-77 |

| 9.14.8. Normalize Instructions                                                                                                           | 9-77 |

| 9.14.8.1. Bit Normalize - BN 72,12                                                                                                       | 9-77 |

| 9.14.8.2. Byte to Bit Normalize - BBN 72,14                                                                                              | 9-77 |

| 9.14.9. Single Character Instructions                                                                                                    | 9–78 |

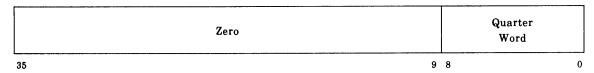

| 9.14.9.1. Load A Quarter Word - LAQW 07,04                                                                                               | 9–78 |

| 9.14.9.2. Store A Quarter Word - SAQW 07,05                                                                                              | 9-78 |

| 0.15 73 4' 1 4'                                                                                                                          |      |

| 9.15. Executive Instructions                                                                                                             | 9-79 |

| 9.15.1. Initiate Maintenance Interrupt - IMI 72,00                                                                                       | 9-79 |

| 9.15.2. Prevent All Interrupts and Jump - PAIJ 72,13                                                                                     | 9-79 |

| 9.15.3. Load Dayclock - LDC 73,14,10                                                                                                     | 9-80 |

| 9.15.4. Diagnostics                                                                                                                      | 9–80 |

| 9.15.4.1. Microdiagnostic C - MDC 73,14, 16<br>9.15.4.2. Reserved Operation Codes - 73,14, 14, 15, 17                                    | 9-80 |

| 9.15.4.2. Reserved Operation Codes - 73,14, 14, 15, 17                                                                                   | 9-81 |

| 9.15.5. Select Interrupt Locations - SIL 73,15,00<br>9.15.6. Load Breakpoint Register - LBRX 73,15,02                                    | 9-81 |

| 9.15.6. Load Breakpoint Register - LBRX 73,15,02                                                                                         | 9-81 |

| 9.15.7. Load Quantum Timer - LQT 73,15,03                                                                                                | 9-82 |

| 9.15.8. Initiate Interprocessor Interrupt - IIIX 73,15,04                                                                                | 9-82 |

| 9.15.9. Store Processor ID - SPID 73,15,05                                                                                               | 9-82 |

| 9.15.10. Clear Support Controller - Clear SC 73,15,06                                                                                    | 9-83 |

| 9.15.11. Load Base - LB 73,15,10                                                                                                         | 9-83 |

| 9.15.12. Load Limits - LL 73,15,11                                                                                                       | 9-83 |

| 9.15.13. Load Addressing Environment - LAE 73,15,12                                                                                      | 9-84 |

| 9.15.14. Store Quantum Timer - SQT 73,15,13                                                                                              | 9-84 |

| 9.15.15. Load Designator Register - LD 73,15,14                                                                                          | 9-84 |

| 9.15.16. Store Designator Register - SD 73,15,15                                                                                         | 9-84 |

| 9.15.17. User Return - UR 73,15,16                                                                                                       | 9-84 |

| 9.15.18. Input/Output Instructions                                                                                                       | 9–85 |

| 9.16. Invalid Function Codes                                                                                                             | 9-85 |

| Annondix A Abbreviations Definitions and Sumbala                                                                                         | A -  |

| Appendix A. Abbreviations, Definitions, and Symbols                                                                                      | A-1  |

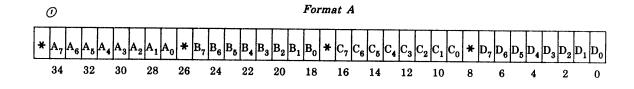

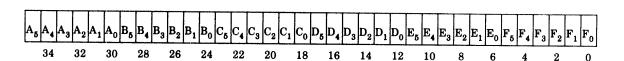

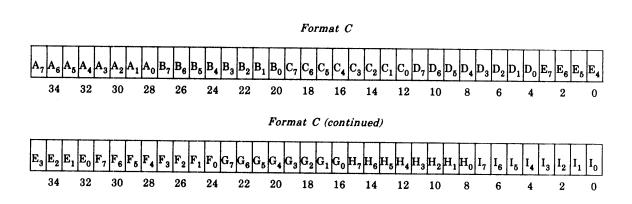

| Appendix B. Summary of Word Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B-1                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Appendix C. Instruction Repertoire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C-1                                                                                                                 |

| Appendix D. Code Conversions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D-1                                                                                                                 |

| D.1. ASCII and Fieldata Code Conversion Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D-1                                                                                                                 |

| D.2. Special Characters in ASCII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D-6                                                                                                                 |

| Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| User Comment Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

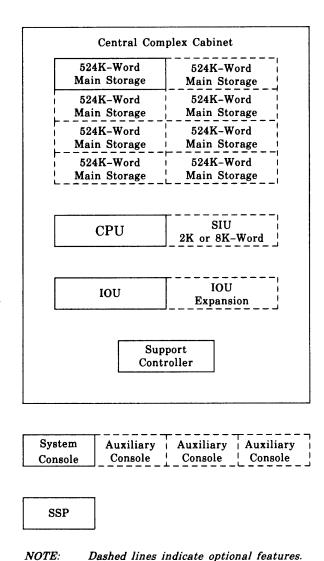

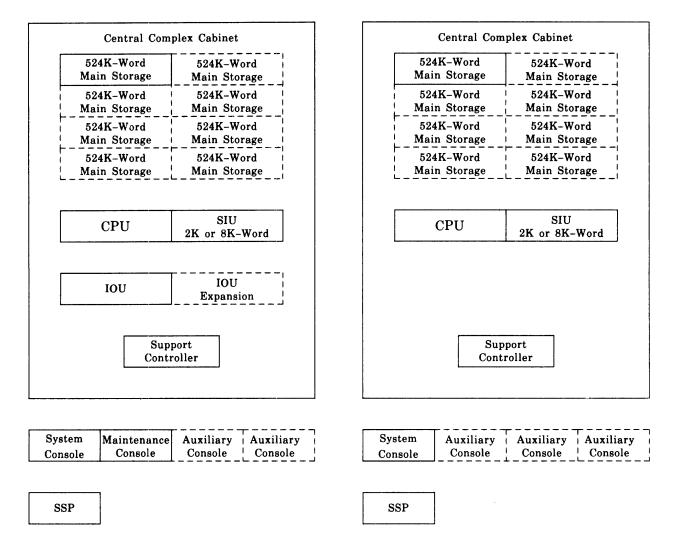

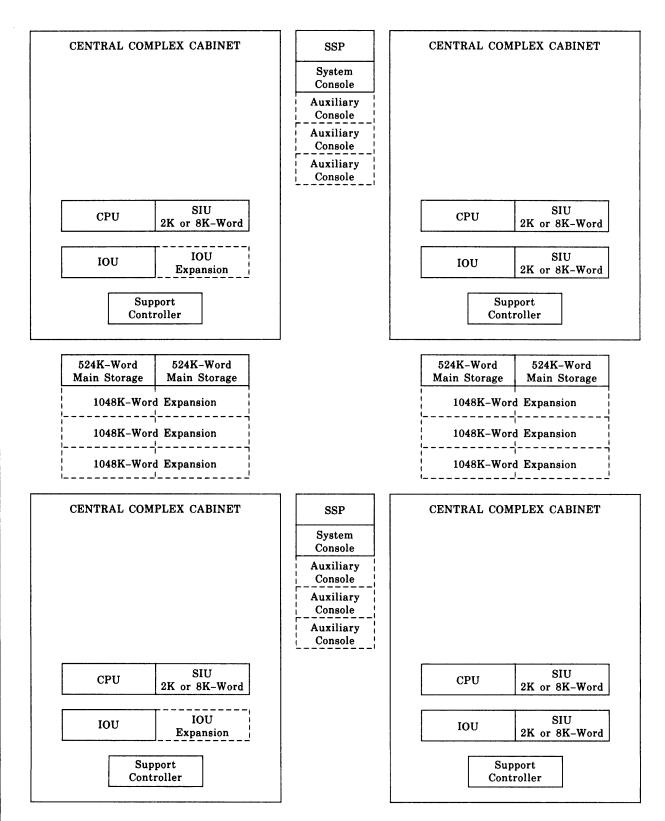

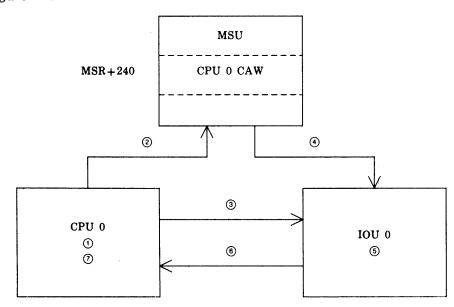

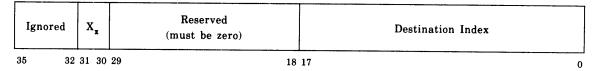

| Figure 2-1. Unit Processing System Configuration 1x1 Figure 2-2. Dual Processor Configuration 2x1 Figure 2-3. Multiprocessor Configuration (4x4) Figure 3-1. Data Transfers from Storage Figure 3-2. Data Transfers to Storage Figure 4-1. 1100/70 Input/Output Unit Figure 4-2. Block Multiplexer Channel Compared to Word Channel Figure 4-3. I/O Instruction Execution Simplified Block Diagram Figure 5-1. SSP Configuration and Interfaces Figure 6-1. Internal SIU Storage Check Interrupt Status Format Figure 6-2. Storage Boundary and Address Format for Internal Storage Figure 6-3. Storage Boundary and Address Format for External Storage Figure 6-5. MSU Status Word Format Figure 7-1. Basic Designator Register States Figure 7-3. Base Value Selection | 2-8<br>2-9<br>2-10<br>3-15<br>3-16<br>4-2<br>4-4<br>4-9<br>5-2<br>6-7<br>6-8<br>6-16<br>6-17<br>6-18<br>7-7<br>7-11 |

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| Table 2-1. 1100/70 Systems Configuration Component Table 3-1. Instructions that Condition the Carry and Overflow Designators Table 3-2. Sign Bit Combinations That Set Carry Designator Table 3-3. Single-Precision Floating-Point Characteristic Values and Exponent Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-11<br>3-4<br>3-5<br>3-7                                                                                           |

| Table 3-4. Double-Precision Floating-Point Characteristic Values and Exponent Values  Table 4-1. MSU Data Format - 36-Bit Format, Forward Operation  Table 4-2. MSU Data Format - 36-Bit Format, Backward Operation  Table 5-1. System Profile Parameters  Table 6-1. 1100/70 Fixed Address Assignments  Table 6-2. GRS Register Assignments 0 Through 63  Table 6-3. GRS Register Assignments 64 Through 127  Table 8-1. Interrupt Priority  Table 9-1. Truth Table for Logical OR, XOR, and AND  Table C-1. Mnemonic/Function Code Cross-Reference  Table C-2. Instruction Repertoire  Table C-3. Octal vs Mnemonic Instruction Code  Table D-1. Fieldata to ASCII Code Conversion  Table D-2. ASCII to Fieldata Code Conversion                                        | 3-7<br>4-23<br>4-24<br>5-5<br>6-25<br>6-27<br>6-28<br>8-2<br>9-46<br>C-1<br>C-4<br>C-18<br>D-2<br>D-4               |

### 1. Introduction

### 1.1. General

The SPERRY 1100/70 Systems are general purpose, medium to high performance, unit processor, dual processor, or multiprocessor systems incorporating the latest advances in computer design, system organization, and programming technology. Although the 1100/70 Systems differ from other Series 1100 Systems in some respects, software compatibility with the other systems is maintained. The various components of the system are designed as separate logical units providing maximum functional modularity. The multiprocessing capabilities are an integral part of the system. The processing unit can perform numerous tasks simultaneously under the control of a single SPERRY Series 1100 Executive System. The flexible modular structure enables a system to be tailored to fit a user's individual needs.

Three basic processing systems for the 1100/70 are:

- unit processor system (one Central Processing Unit (CPU) and one Input/Output Unit (IOU), 1x1);

- dual processing system (two CPUs and one IOU, 2x1); and

- multiprocessing system (two to four CPUs and two to four IOUs, 2x2, 3x3, 4x2, 4x4).

Each processing system has a variety of models available: the unit processor system has Models B1, C1, C2, E1, E2, H1, and H2; the dual processor and multiprocessor systems have Models E1, E2, H1, and H2.

### 1.2. Scope

This manual provides reference information to be used by the programmer of an 1100/70 System. Detailed information is provided on the CPU, IOU, Storage Interface Unit (SIU), Main Storage Unit (MSU), and System Support Processor (SSP). Section 2 includes a brief description of all the components in the 1100/70 Systems.

# 2. Systems Description

### 2.1. General

The SPERRY 1100/70 Systems incorporate the latest advances in design technology and system organization. Like the other members of the Series 1100 family, the 1100/70 Systems provide an efficient multiprocessor capability that allows Central Processing Units (CPUs) to perform multiple tasks simultaneously under the control of a single common Executive System. The 1100/70 Systems are available in three basic modules: the unit processor (1x1), the dual system processor (2x1), and the multiprocessor (2x2, 3x2, 3x3, 4x2, 4x4) configuration. Principal features of the 1100/70 Systems are:

- single or multiple CPUs, Input/Output Units (IOUs), and Main Storage Units (MSUs);

- common access to most system components in multiple CPU/IOU/MSU configurations;

- Input/Output (I/O) operations controlled by the IOU;

- byte- and word-oriented I/O channels:

- large, modular semiconductor main storage (8,388,608 words maximum);

- an optional CPU-associated high-speed buffer storage (2048 or 8192 words per CPU);

- an optional extended instruction set;

- comprehensive error checking and correction facilities:

- an optional hardware performance monitor;

- system component redundancy:

- central complex and optional subsystem partitioning;

- an automated hardware diagnostic/prognostic system;

- extensive storage and component protection facilities for security and servicing;

- partial-, full-, and double-word addressability;

- an optional compatible channel interface feature;

- program address relocatability; and

- a continuously evolving comprehensive Operating System.

### 2.2. System Components

The system configuration can vary depending on customer needs. The major hardware components of 1100/70 Systems are:

- Central complex cabinet (can contain one CPU, one IOU, one SIU, one MSU and one SC)

- Central Processing Unit (CPU)

- Input/Output Unit (IOU)

- Main Storage Unit (MSU)

- Storage Interface Unit (SIU)

- Support Controller (SC)

- System Support Processor (SSP)/Console

- System Console

- Attached Virtual Processor (AVP)

- Auxiliary storage and peripheral subsystems

- Onsite and remote communications subsystems.

A unit processor contains one central complex cabinet. Dual and multiprocessor systems can contain from two to four central complex cabinets and can be divided into two clusters.

A cluster consists of one or two central complex cabinets. Each cluster has access to the external main storage. The IOUs in a cluster can only access the CPUs in the same cluster.

An SIU is required for each CPU in a dual or multiprocessor system. Systems with one or two central cabinets use main storage located within the central complex cabinet. Systems with three or four central complex cabinets require external main storage.

### 2.2.1. Central Processing Unit (CPU)

The CPU executes all control and arithmetic functions in the system by a combination of hard-wired logic and firmware. An 1100/70 System may contain one to four CPUs. The CPU contains interfaces to an MSU or SIU, two IOUs, two SSPs, and to other CPUs.

Capabilities of the CPU include:

- 116 nanoseconds basic cycle time;

- 128-word General Register Stack (GRS);

- an instruction/operand prefetch;

- an addressing range of 16 million 36-bit words;

- relative addressing providing program segmentation and storage protection;

- four bank addressing;

- extensive fault detection and instruction retry capability;

- an optional SIU, providing performance improvement and interface to two MSUs;

- an optional extended instruction set feature; and

- an optional performance monitor feature.

1

1

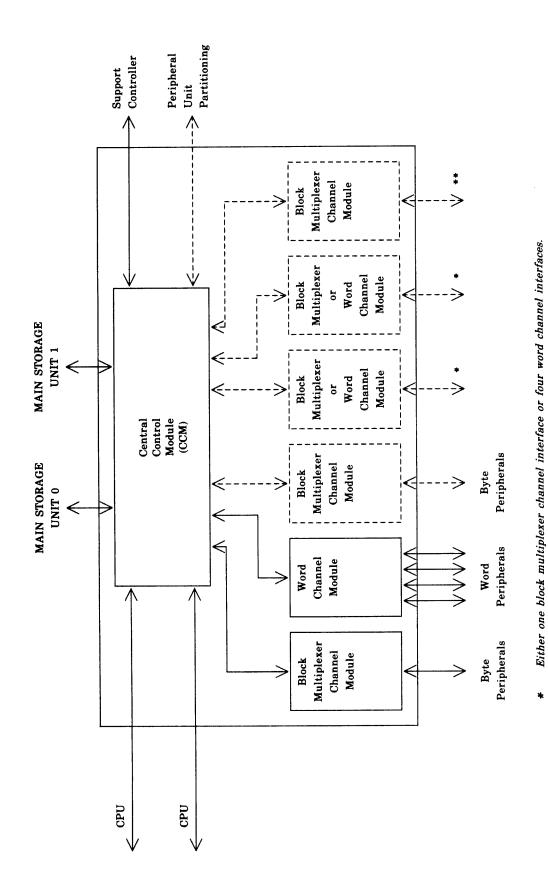

### 2.2.2. Input/Output Unit (IOU)

An 1100/70 System contains one to four IOUs. Under CPU direction, the IOU controls all transfers of data between main storage and peripheral devices. The IOU consists of a Central Control Module (CCM) and up to six channel modules. The CCM provides independent control paths to one or two CPUs (within the same cluster in a dual or multiprocessor system) and one or two SSPs, and data paths to one or two MSUs. Both block multiplexer and Series 1100 word channel modules are included for (I/O) transmissions.

### Capabilities of the IOU include:

- a capacity of up to three block multiplexer channel modules and up to three word channel modules, or five block multiplexer channel modules and one word channel module;

- Internally Specified Index (ISI) or Externally Specified Index (ESI) transfer modes on word channels;

- parity generation/checking capability on all word channels operated in ISI mode;

- optional subsystem partitioning features;

- channel transfer rates of

- 1.6 million bytes (371k words) per second on a block multiplexer channel,

- 718k words per second (maximum) on a single word channel interface,

- 1.4 million words per second (maximum input) aggregate for four word channel interfaces (one word channel module),

- 86k words per second (maximum output) aggregate for four word channel interfaces (one word channel module),

- direct interface to storage;

- channel operation controlled by channel command words; and

- an optional compatible channel interface feature.

### 2.2.3. Main Storage Unit (MSU)

The 1100/70 System offers two types of main storage.

One type is located in the central complex cabinet, which has a minimum of 524,288 (524K) words, expandable in 524K-word increments to a maximum of 4,194,304 (4194K) words per cabinet. Main storage located in the central complex cabinet can only be used with 1100/71 and 1100/72 Systems (see Table 2-1).

A second type of main storage is located in a free-standing MSU cabinet, which has a minimum of 1,048,576 (1048K) words, expandable in 1048K-word increments to a maximum of 4194K words per cabinet. One or two free-standing MSU cabinets can be used on a system for a maximum of 8,388,604 (8388K) words. The free-standing MSU cabinet is required with the 1100/73 and 1100/74 Systems.

The two types of storage cannot be used on the same system.

The control section of the MSU provides requester (CPU or SIU, IOU, and SSP) priority circuitry.

Capabilities of the MSU include:

- 43-bit word (36 data bits + 7 error correction code bits) internal format;

- 38-bit word (36 data bits + 2 parity bits) format at the requester interface;

- capacity from 524K up to 4194K words per MSU;

- single- or 4-word read, single- and partial-word write;

- single- and double-bit error detection and single-bit error correction;

- application partitioning by requester interface and by 262K-word granularity;

- scan/set interface for diagnostic/prognostic testing;

- an internal refresh;

- internal priority circuitry; and

- internal exerciser for offline operation.

### 2.2.4. Storage Interface Unit (SIU)

An SIU contains either 2048-word (2K) or 8195-word (8K) of high speed buffer storage and is interposed between the CPU and MSU. The Models B and C Systems do not contain an SIU. The Model E Systems contain a 2K-word SIU and the Model H Systems contain an 8K-word SIU in each central complex cabinet. An SIU connects to both MSUs in a multiprocessor configuration. The SIU provides dedicated service to one CPU and interfaces with one or two MSUs, and one or two SSPs.

Capabilities of the SIU include:

- single-word wide interface to main storage (one storage cycle)

- four words contained in the data block are transmitted in word-serial fashion from main storage to the SIU (four storage cycles)